# i4000

Quad M-module carrier for VMEbus

Hardware Manual

#### Copyright statement: Copyright © 1996 by AcQuisition Technology B.V. - OSS The Netherlands

All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of AcQuisition Technology B.V.

#### Disclaimer:

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. AcQuisition Technology B.V. makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Furthermore, AcQuisition Technology B.V. reserves the right to make changes to any product herein to improve reliability, function or design, without obligation of AcQuisition Technology B.V. to notify any person of such revision or changes. AcQuisition Technology B.V. does not assume any liability arising out of applications or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

Tel: +31 412 651055

Fax: +31 412 651050

Printed in The Netherlands.

### **Contents**

| 1. | . Usino | g the manual                                   |

|----|---------|------------------------------------------------|

|    | 1.1.    | Validity of this manual                        |

|    | 1.2.    | Ordering considerations 4                      |

|    |         |                                                |

| 2. |         | duction 5                                      |

|    | 2.1.    | Technical overview 5                           |

|    | 2.2.    | Block diagram 5                                |

| 2  | \       | ava intenface                                  |

| ა. |         | ous interface                                  |

|    | 3.1.    | Address interface                              |

|    | 3.2.    | The interrupter                                |

|    | 3.3.    | Dipswitch locations                            |

|    | 3.4.    | VMEbus P1 connector assignments                |

| 4  | . Modi  | ule installation                               |

| •  | 4.1.    | Mounting the module                            |

|    | 4.2.    | P2 connector assignments                       |

|    | 4.3.    | i4000 - module interface connector assignments |

|    | 1.0.    | Troop module interface confidence assignments  |

| 5. | . Softw | vare issues                                    |

|    | 5.1.    | Address mapping                                |

|    | 5.2.    | The interrupt controller                       |

|    | 5.2.1   | •                                              |

|    | 5.2.2   | ·                                              |

|    | 5.2.3   | ·                                              |

|    | 5.2.4   |                                                |

|    | 5.2.5   | 3                                              |

|    |         |                                                |

| 6. | . Anne  | x                                              |

|    | 6.1.    | Bibliography                                   |

|    | 6.2.    | Difference compared to former versions         |

|    | 6.3     | Technical data 18                              |

### 1. Using the manual

This manual serves as instruction for the operation of the VMEbus board i4000, the connection of peripheral devices and the integration in a VMEbus system. Furthermore it gives the user additional information for special applications and configurations of the assembly.

Detailed information concerning the individual assemblies (data sheets etc.) are not part of this manual. In the annex you will find a bibliography.

This manual describes the hardware of the assembly.

Notes concerning the nomenclature:

Hex numbers are marked with a leading "\$"-sign: for example: \$800000 or \$BFFFFF.

Active-low signals are represented by a trailing asterisks (i.e. IACK\*).

### 1.1. Validity of this manual

The contents of this manual is valid for i4000 revision 2.x

# 1.2. Ordering considerations

The i4000 comes in two types: with, or without the P2 connector mounted.

| Order Code | Description                        |

|------------|------------------------------------|

| i4000/P2   | i4000 with P2 connector mounted    |

| i4000/NP2  | i4000 without P2 connector mounted |

One should NOT apply the i4000/P2 when:

- a P2 backplane is in the VMEbus rack, or

- galvanic isolation is required.

NOTE: P2 connector on the i4000 is **NOT** VMEbus compatible !!!

Tel: +31 412 651055

Fax: +31 412 651050

### 2. Introduction

The i4000 is a modular passive peripheral-controller for the VME-bus. Up to four M-modules can be connected to the board to form a peripheral-controller..

### 2.1. Technical overview

The i4000 has the following features:

- 4 M-module slots

- · One VMEbus slot needed

- short or standard VMEbus addressing (A16/A24)

- byte or word data transfer (D08/D16)

- D08(O) VMEbus interrupter

- peripheral I/O connections either up front or via the VME-P2 connector.

- Additional mounting holes to secure the modules

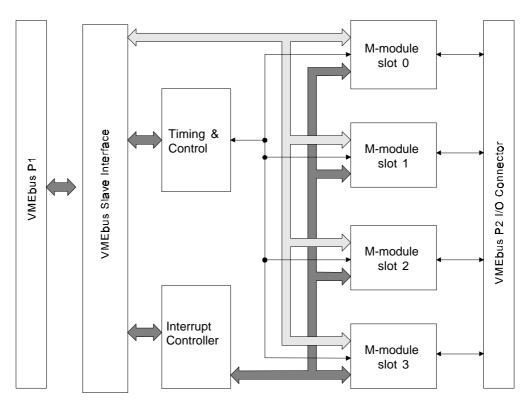

### 2.2. Block diagram

Figure 1 i4000 Block Diagram

### 3. VMEbus interface

### 3.1. Address interface

The i4000 can be selected to accept either short addressing, using 16 bit addresses (A16) or standard addressing, using 24 bit addresses (A24).

When using short addressing up to 32 i4000 boards can be put in a single VMEbus system since the lower 11 address lines (A0-A10) are used internally on the i4000. If standard addressing is used, a larger address space is available to select the board.

The memory space occupied by the i4000 is \$800 bytes long. This memory space is equally spread across the four modules. so each module occupies \$200 bytes. From these \$200 bytes address space half is used by the interrupt controller. The address space for each module is therefore \$100 bytes long (8 bit addressing).

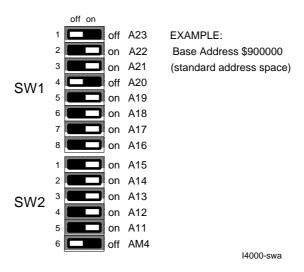

The address space of the i4000 is selectable using dip switches (SW1 and SW2) which are accessible even when the four module slots are occupied. When a switch is "on" the corresponding address line is a logical "zero" and when a switch is "off" the corresponding address line is "one".

Address modifier AM4 can be used to select either standard or short memory addressing. If AM4 is "one" (the switch is in the off position) standard addressing is selected. If AM4 is "zero" (switch on) short addressing is selected. When using short addressing the address lines A16-A23 are don't cares.

Tel: +31 412 651055

Figure 2 Address Selection

Fax: +31 412 651050

### 3.2. The interrupter

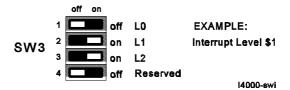

The i4000 has a special interrupter which is largely compatible with the M68C153. The interrupter is a so called D08(O) type interrupter which means that the interrupter during an interrupt acknowledge cycle will put a status byte on the data line D0-D7. The interrupter has one interrupt level (IRQ1-IRQ7) selectable by dip switches (SW3) for all the modules. Each module can generate its own vector.

There are two classes of interrupters which are both supported by the i4000: release on acknowledge (ROAK) or release on register access (RORA). The ROAK interrupter negates its interrupt request line in response to an interrupt acknowledge cycle. This mechanism will work with all handlers. The RORA interrupter releases its request when the handler accesses an on-board register during the interrupt service routine. The handler performs the acknowledge cycle but the interrupter does not immediately negate its request. Sometime during the service routine the handler will have to write to a register on the interrupter which causes it to negate the request.

Figure 3 Interrupt request Level

Fax: +31 412 651050

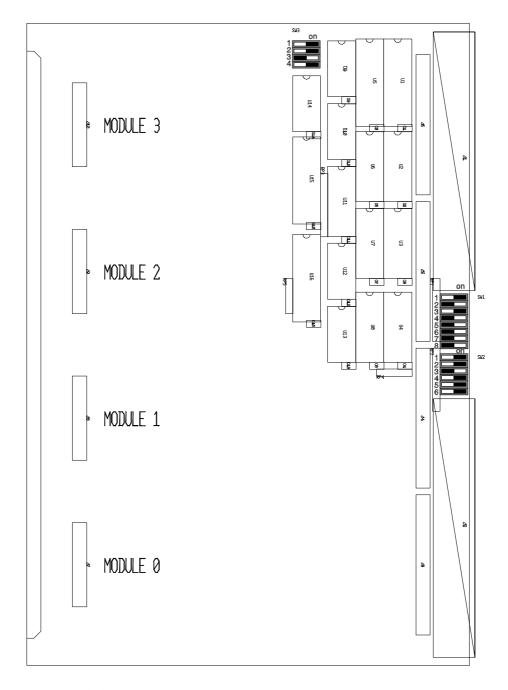

## 3.3. Dipswitch locations

The location of the dip switches to select the base address (SW1 and SW2) and the dip switch to select the interrupt request level (SW3) can be found at the following locations:

Figure 4 Dip switch locations

# 3.4. VMEbus P1 connector assignments

The following table provides signal names for the VMEbus P1 connector as used by the i4000. (The connector consists of three rows of pins labelled rows a, b and c.)

| Pin      | Row A       | Row B             | Row C       |

|----------|-------------|-------------------|-------------|

| 01       | D00         |                   | D08         |

| 02       | D01         |                   | D09         |

| 03       | D02         | 5 C C I I I I     | D10         |

| 04       | D03         | BG0IN*            | D11         |

| 05<br>06 | D04<br>D05  | BG0OUT*<br>BG1IN* | D12         |

| 06<br>07 | D05         | BG1IN<br>BG1OUT*  | D13<br>D14  |

| 08       | D06<br>D07  | BG1001<br>BG2IN*  | D14<br>D15  |

| 09       | GND         | BG2NV<br>BG2OUT*  | GND         |

| 10       | SYSCLK      | BG3IN*            | GIVD        |

| 11       | GND         | BG3OUT*           |             |

| 12       | DS1*        | 2000.             | RESET*      |

| 13       | DS0*        |                   | LWORD*      |

| 14       | WRITE*      |                   | AM5         |

| 15       | GND         |                   | A23         |

| 16       | DTACK*      |                   | A22         |

| 17       | GND         |                   | A21         |

| 18       | AS*         |                   | A20         |

| 19       | GND         |                   | A19         |

| 20       | IACK*       | GND               | A18         |

| 21       | IACKIN*     |                   | A17         |

| 22       | IACKOUT*    | CND               | A16         |

| 23<br>24 | AM4<br>A07  | GND<br>IRQ7*      | A15<br>A14  |

| 25       | A07<br>A06  | IRQ6*             | A14<br>A13  |

| 26       | A05         | IRQ5*             | A13<br>A12  |

| 27       | A04         | IRQ4*             | A12<br>A11  |

| 28       | A03         | IRQ3*             | A10         |

| 29       | A02         | IRQ2*             | A09         |

| 30       | A01         | IRQ1*             | A08         |

| 31       | -12V        |                   | +12V        |

| 32       | +5 <b>V</b> | +5V               | +5 <b>V</b> |

### 4. Module installation

### 4.1. Mounting the module

A maximum of four modules can be fitted on the i4000 base board. To plug in a module slide the module from above under an angle on top of the i4000 and first position the 25-pole sub-D connector through the openings in the front cover. Then position the 24-pole female header on top of the corresponding header on the base board. Push the module until the 40-pole header connector is positioned and press the module with care in its place.

The module can be secured in its position using two or four screws (M3 \* 5mm). The older modules only have mounting provisions for the two screws on the 25-pole sub-D connector but the newer modules have two additional screws to secure the module.

### 4.2. P2 connector assignments

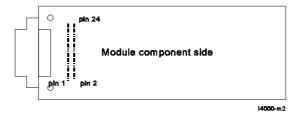

Peripherals can be connected to M-modules in two ways. On the front side of the module a 25-pole sub-D connector (or mechanically equivalent) can be used to connect cables on the front panel of the VMEbus base board. Alternatively, a 24-pole header connector interfaces the I/O signals to the base board where they are connected to the VMEbus P2 connector.

In 32 bit VMEbus systems the backplane for the P2 connector must either be removed for the i4000 slot or an i4000 without the P2 connector must be ordered. In that case the peripherals can be connected to the M-module up front.

Figure 5 Orientation of 24-pole header connector

Every M-module has 24 pins of the P2 connector assigned. Four modules on a base board can then use this I/O path.

This division into four pads of the P2 connector enables so called "module connector" to be plugged into the back of a 96-way shroud, mounted on the "P2-backplane". On the 96-way connector 3 pins are not used for every module. Several manufacturers produce these "module connectors, which can be coded and sometimes have latches.

Tel: +31 412 651055

Corresponding pins on the 96-way P2 to 24-way header connector on module.

| pin                                                                                                                                                                                                | Row c                                                                                                                                                                                                                                                                                                                                                                    | Row b                                                                                                                                                                                                                                                                                                                               | Row a                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01<br>02<br>03<br>04<br>05<br>06<br>07<br>08<br>09<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>31<br>32 | 3<br>6<br>9<br>12<br>15<br>18<br>21<br>(24)<br>3<br>6<br>9<br>12<br>15<br>18<br>21<br>(24)<br>3<br>6<br>9<br>12<br>15<br>18<br>21<br>(24)<br>3<br>6<br>9<br>12<br>15<br>18<br>21<br>(24)<br>3<br>6<br>9<br>12<br>15<br>18<br>21<br>(24)<br>3<br>6<br>9<br>12<br>15<br>15<br>16<br>16<br>17<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18 | 2<br>5<br>8<br>11<br>14<br>17<br>20<br>(23)<br>2<br>5<br>8<br>11<br>14<br>17<br>20<br>(23)<br>2<br>5<br>8<br>11<br>14<br>17<br>20<br>(23)<br>2<br>5<br>8<br>11<br>14<br>17<br>20<br>(23)<br>2<br>5<br>8<br>11<br>14<br>17<br>20<br>(23)<br>2<br>5<br>8<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>1 | 1<br>4<br>7<br>10<br>13<br>16<br>19<br>(22)<br>1<br>4<br>7<br>10<br>13<br>16<br>19<br>(22)<br>1<br>4<br>7<br>10<br>13<br>16<br>19<br>(22)<br>1<br>4<br>7<br>10<br>13<br>16<br>19<br>(22)<br>1<br>4<br>7<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10<br>10 |

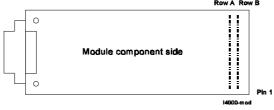

# 4.3. i4000 - module interface connector assignments

The interface between the i4000 baseboard and a M-Module is realised with a 20-pole male header connector.

| Pin | Row A  | Row B       |

|-----|--------|-------------|

| 01  | CS*    | GND         |

| 02  | A01    | +5 <b>V</b> |

| 03  | A02    | +12V        |

| 04  | A03    | -12V        |

| 05  | A04    | GND         |

| 06  | A05    | DREQ*       |

| 07  | A06    | DACK*       |

| 80  | A07    | GND         |

| 09  | D08    | D00         |

| 10  | D09    | D01         |

| 11  | D10    | D02         |

| 12  | D11    | D03         |

| 13  | D12    | D04         |

| 14  | D13    | D)5         |

| 15  | D14    | D06         |

| 16  | D15    | D07         |

| 17  | DS1*   | DS0*        |

| 18  | DTACK* | WRITE*      |

| 19  | IACK*  | IRQ*        |

| 20  | RESET* | SYSCLK      |

Location of the 24-pole header connector on the M-module:

Figure 6 Orientation of connector on module

### 5. Software issues

### 5.1. Address mapping

As mentioned before the address space occupied by the i4000 board is \$800 bytes (A0-A10). These \$800 bytes are divided into 4 identical spaces. Every \$200 bytes block is assigned to a module slot. The first \$100 byte address space is assigned to the module itself and the second \$100 byte is used for the access part of the interrupt controller.

Using this method of address decoding provides an identical address map for each module on the i4000 board. This makes writing the software easier since just the base address of the module, not the base address of the i4000 has to be known. Every module has its own Interrupt-Vector and Interrupt-Control register. The \$100 bytes from each module used to access the interrupt controller are not completely decoded. Both registers of the Interrupt controller are mirrored several times within the \$100 bytes address space. If the module itself the \$100 bytes completely decodes, depends on the used module.

Address Map of the i4000:

| \$000\$0ff<br>\$101<br>\$103 | Module<br>Control register (CR0)<br>Vector register (VR0) | Module 0 |

|------------------------------|-----------------------------------------------------------|----------|

| \$200\$2ff<br>\$301<br>\$303 | Module<br>Control register (CR1)<br>Vector register (VR1) | Module 1 |

| \$400\$4ff<br>\$501<br>\$503 | Module<br>Control register (CR2)<br>Vector register (VR2) | Module 2 |

| \$600\$6ff<br>\$701<br>\$703 | Module<br>Control register (CR3)<br>Vector register (VR3) | Module 3 |

The base address of a module can be calculated using the following formula:

ModuleBaseAddress = i4000BaseAddress + ModuleNumber \* \$200

#### **EXAMPLE:**

The installed base address of the i4000 is \$800000. A module is fitted into slot 2. The module base address is then \$800000 + 2 \* \$200 = \$800200. When using a 32 bit master which accesses the standard address space at address \$ffxxxxxxx, then the

Tel: +31 412 651055

Fax: +31 412 651050

module will be accessed at address \$ff800200. The corresponding interrupt control register address is then \$ff800301.

### 5.2. The interrupt controller

### 5.2.1. Functional description

The Interrupt controller used with the i4000 is largely compatible the MC68153 Interrupt controller from Motorola.

The interrupt controller provides a means for the modules to ask for an interrupt of the processor activity and receive service from the processor. The Interrupt controller on the i4000 acts as an interface device requesting and responding to interrupt acknowledge cycles for up to 4 independent modules.

### 5.2.2. Register description

The Interrupt controller of the i4000 contains 8 programmable registers. There are four control registers (CR0-CR3) that govern operation of the Interrupt controller and four vector registers (VR0-VR3) that contain the vector data used during an interrupt acknowledge cycle. Every module is assigned one register pair.

Fax: +31 412 651050

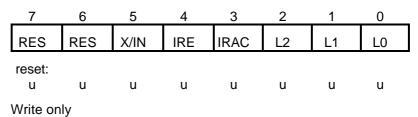

### 5.2.3. Control register

Control Register

### L2-L0 (Interrupt level, dummy bits)

The least significant 3-bit field of the register determines the level at which an interrupt will be generated.

These three bits are NOT used in the i4000 interrupt controller since the interrupt level for all the four modules is selected via dip switches. However to maintain software compatibility with the A201 it is advisable to program these 3 bits with the same interrupt level as the dip switches.

#### **IRAC (Interrupt Auto-Clear)**

If the IRAC is set (Bit 3), IRE (Bit 4) is cleared during an interrupt acknowledge cycle responding to this request. This action of clearing IRE disables the module interrupt request. To re-enable the module interrupt request associated with this register, IRE must be set again by writing to the control register.

#### IRE (Interrupt enable)

This field (Bit 4) must be set (high level) to enable the module interrupt request associated with the control register. Thus, if the module asserts IRQ and IRE is cleared, no interrupt request to the VMEbus will be generated.

#### X/IN\* (External/Internal)

Bit 5 of the control register determines the response of the i4000 interrupt controller during an interrupt acknowledge cycle. If the X/IN\* bit is clear (low level) the Interrupt Controller will respond with vector data and a DTACK\* signal, i.e., an internal response. If X/IN\* is set, the vector is not supplied and no DTACK\* is given by the Interrupt Controller, i.e., an external module should respond.

#### **RESERVED**

These two bits are not used in the current implementation of the Interrupt Controller and reserved for future use.

Fax: +31 412 651050

### 5.2.4. Vector registers

Each module interrupt input has its own associated vector register. Each register is 8 bits wide and supplies a data byte during its interrupt acknowledge cycle if the associated External/Internal (X/IN\*) control register bit is clear (zero). This data can be status, identification, or address information depending on system usage. The information is programmed by the system user.

### 5.2.5. Interrupt controller reset

When a VMEbus reset is applied, the control registers of the i4000 interrupt controller are set to all zeros (low). The vector registers however are uninitialized and should be programmed before use.

### 6. Annex

### 6.1. Bibliography

Specification for M-module interface and physical dimensions:

M-module specification manual, revision 2.2, M-Module Manufactures Group.

#### Interrupt controller:

MC68153 datasheet, Motorola Semiconductors, Inc

### 6.2. Difference compared to former versions

#### Revision 1.0

First release.

#### Revision 1.1

Bug fixed concerning Interrupt level switch. Most significant and least significant bit are swapped.

#### Revision 2.0

- Jumpers removed

- Power and ground plane

- IACK's synchronized

Fax: +31 412 651050

### 6.3. Technical data

#### Module number:

Up to four modules can be plugged onto the baseboard. Virtually unlimited number of baseboards in one VME system.

#### Interrupt Controller:

Separate interrupt handling for each module.

#### VMEbus connection:

A24/D16 Slave interface D08(O) Interrupter

#### Power supply:

- +5VDC (+-5%), typical 300mA (without modules)

- +12VDC, 0mA (without modules)

- -12VDC, 0mA (without modules)

### Temperature range:

Operating: 0..+60 degr. Celsius Storage: -20..+70 degr. Celsius

### Humidity:

Class F, non-condensing.